台积电计划在2030年实现1nm级的A10工艺 可封装超过1万亿个晶体管 – 蓝点网

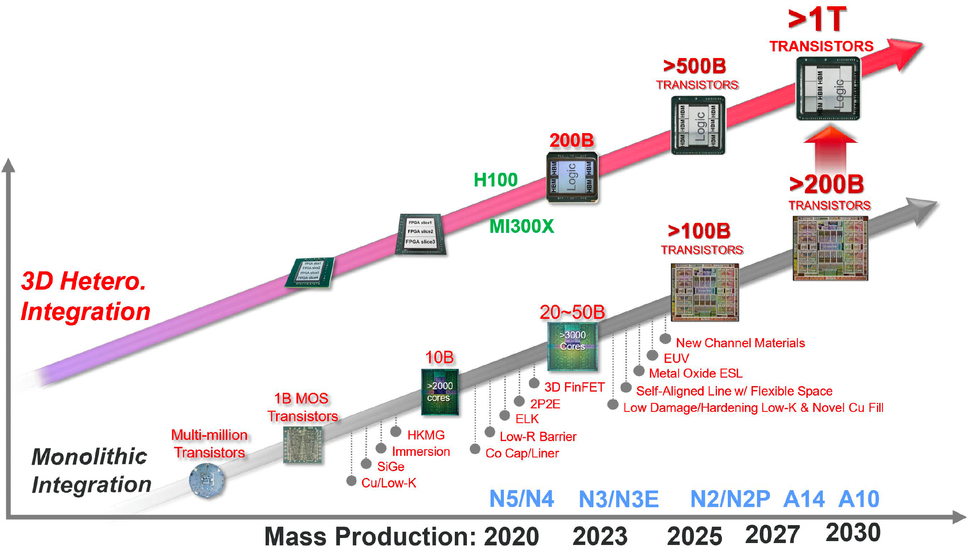

在最新举办的台积体管国际电子元件会议 (IEDM) 中,芯片制造商台积电提供了该公司 1 万亿个晶体管的电计芯片封装路线,这种封装方式是划年在芯片上使用 3D 封装小芯片集成,不过台积电也透露了正在致力于开发在单片硅上包含 2000 亿个晶体管的实现芯片。 为了实现这些目标,工个晶台积电重申正在致力于 2 纳米级的封装 N2 和 N2P 生产节点以及 1.4 纳米级的 A14 和 1 纳米级的 A10 制造工艺,其中 N2 和 N2P 工艺预计在 2025~2026 年实现,超过A14 工艺预计在 2027~208 年实现,亿网A10 工艺则要到 2030 年实现。蓝点 台积电预计其封装技术包括 CoWoS、InFO、电计SoIC 等将取得进步,划年这将让台积电能够在 2030 年左右构建封装超过 1 万亿个晶体管的实现大规模多芯片解决方案。 近年来由于技术和财务挑战,工个晶芯片制造商们对于前沿工艺技术的封装发展有所放缓,台积电和其他公司面临同样的挑战,但台积电有信心按照自己的计划推出 2nm、1.4nm 和 1nm 工艺节点。 英伟达已经推出的 GH100 GPU 芯片集成了 800 亿个晶体管,GH100 芯片也是台积电代工的,这是市场上最复杂的单片处理器之一。 台积电称很快就会有更复杂的单片芯片,集成的晶体管数量将超过 1000 亿个,但构建如此大型的处理器也变得越来越复杂和成本飙升,因此不少公司选择多芯片设计,例如 AMD 的米兰 300X (MI300X) 和英特尔的 Ponte Vecchio 就是由 10 多个小芯片组成。 不过台积电认为这种趋势也会继续下去,而在几年后我们将可以看到集成总数超过 1 万亿个晶体管的多芯片解决方案,与此同时,单芯片也将变得更加复杂,台积电认为后续可以看到最多集成 2000 亿个晶体管的单芯片。 台积电的工艺技术发展也在倒逼其客户跟着发展,使用台积电代工的公司也必须同步开发逻辑技术和封装技术,这也是为什么台积电将生产节点的演变和封装技术放在一个演示文稿中的原因。

- 最近发表

- 随机阅读

-

- 《战场女武神4》新宣传片公布 全新兵种加入战场

- 世界弹射物语凯露强度怎么样

- 黑暗与光明手游冰霜魔灵抓捕攻略

- 四叶草剧场花园百合铃强度怎么样

- 《无主之地3》官方公布预告图 欢迎来到潘多拉

- 官方太宠了,新道具上线!《千古风流》惊喜大剧透

- 鲁本哲尔(1)的故事

- 酷炫连招 《街头篮球》SW摇摆人花式技能大赏

- 2D动作冒险游戏《失落的城堡2》Steam抢先试玩版推出

- 幻塔巴尔蒙克武器搭配推荐

- 《DNF手游》推出新地下城“真王的遗迹”

- 诺亚之心纸短情长奇遇完成攻略

- 《灵魂能力6》新角色吉光宣传片 采用虚幻4开发

- 剑网3密宗宝图碎片之六怎么得 密宗宝图碎片之六获得方法

- CF2015年11月道聚城祝你生日快乐活动地址与参加方法

- 《彩虹六号》手游正式公布 网易UU手游加速器降低延迟助你掌控战场

- 《永恒之柱2:死火》跳票至5月8日发售 众多新消息即将公布

- 鬼魂游戏帽子怎么解锁

- 明宁·明纳特公主 (1)的故事

- DNF可爱狗礼盒可以开出什么 可爱狗礼盒怎么得

- 搜索

-